|

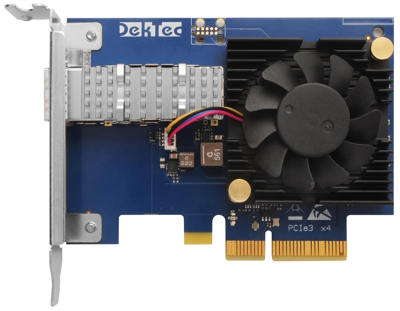

DTA-2125 25G SmartNIC Optimized for SMPTE 2110 Ideal for software-based SMPTE 2110 applications, the DTA-2125 supports up to two uncompressed UHD streams or ten full-HD streams (5 Rx + 5 Tx).

|

Key Characteristics

| Ports |

1x 25G (SFP28)

Also accepts 10G SFP+ modules |

| Standards | SMPTE 2110 SMPTE 2022-5/6

Supports standard IP network stack |

| Hardware Pipes | 5 Rx, 5 Tx |

| PCIe | Gen3 x8, low profile |

| OS | Linux/Windows |

| 🔍 Compare | DekTec SmartNICs |

Networking

| 25G Ethernet | IEEE 802.3by |

| SFP28 | SFF-8431

Direct attach cables not supported |

| IP Protocols | IPv4, IPv6 |

| Jumbo Frames | Supported (up to 9kB) |

| VLAN | IEEE 802.1Q |

SMPTE 2110 Substandards

| ST 2110-10 | System timing model |

| ST 2110-20 | Uncompressed video |

| ST 2110-21 | Video traffic shaping |

| ST 2110-30 | Uncompressed audio |

| ST 2110-31 | AES3 audio |

| ST 2110-40 | Ancillary data (subtitles, …) |

| ST 2110-41 | Fast metadata transport |

| ST 2059-1/2 | Use of PTP in SMPTE 2110 |

You can use raw mode with PTP synchronization to implement any SMPTE 2110 substandard

SMPTE 2022 Substandards

| ST 2022-1 | IP FEC for TS-over-IP |

| ST 2022-2 | TS-over-IP |

| ST 2022-5 | IP FEC for SDI-over-IP |

| ST 2022-6 | SDI-over-IP |

PC Support

| Linux | ≥4.x, 5.x |

| Windows | 10, 11; Server 19, 22, 25 |

| Processor | Core i7 Or equivalent AMD CPU |

Additional Resources

SMPTE 2110 Coding Examples

Explore the AvFifo API examples to kick-start your programming with the DTA-2125.

AvFifo is part of DekTec's DTAPI SDK

for crafting custom applications.

DekTec Software

| StreamXpress | Generate SMPTE-2125 and TS-over-IP test streams |

| StreamXpert | Analyze/view SMPTE-2110 and TS-over-IP streams |

| DTAPI | SDK for DekTec devices with AvFifo API. Use it to create DTA-2110 applications. |

Pricing

| DTA-2125 | € | 1.014 | Stock: 25+ |

| 25G SmartNIC for PCIe with SMPTE 2110 and SMPTE 2022-5/6 hardware acceleration. | |||

| DTA-2125-SLP | € | 1.263 | Stock: 25+ |

| 25G SmartNIC optimized for SMPTE 2110 with StreamXpert Lite and StreamXpress player software. | |||

| DTA-2125-SY-SXP-JXS | € | 3.438 | Stock: 25+ |

| 25G SmartNIC optimized for SMPTE 2110 with SdEye, StreamXpert analyzer and StreamXpress player and JPEG-XS. | |||

Prices exclude applicable sales tax, shipping charges and customs duties. Quantity discounts may be available, please request a quotation.

Features

- Acts as a standard 25G NIC, with hardware acceleration to reduce CPU load for AV-over-IP streaming on Linux and Windows.

- Ten dedicated hardware pipes (5 Rx, 5 Tx) for low-latency transport of uncompressed video.

- AvFifo API for easy creation of SMPTE 2110 and 2022-6 software applications.

- SFP28 slot supporting both 25G and 10G optical or electrical modules.

Applications

-

Ideal for creating SMPTE 2110 solutions entirely in software, while meeting

all timing requirements.

Common use cases include:

- Software encoders, decoders, transcoders

- Playout systems

- Live production mixers

- Monitoring and multiviewer setups

- Recording and compliance solutions

- Custom AV-over-IP applications tailored to your needs

Block Diagram

Outlined below is the block diagram of the DTA-2125's firmware, organized into two pathways: transmission (upper section) and reception (lower section).

The transmission path incorporate three hardware pipes that directly interface with the user application, resulting in excellent performance. Packets from these hardware pipes are multiplexed with those from the software pipes and the standard network stack. A scheduler ensures that each packet is transmitted precisely according to its PTP timestamp.

Conversely, the receive path also integrates 5 hardware pipes directly interfaced with the user application. All remaining packets are dispatched to a software router. This router channels real-time AV streams to the software pipes, while normal standard network traffic is forwarded to the conventional network stack.

Related Products

|

DTA-2110 – 10G SmartNIC Optimized for SMPTE 2110 10G SmartNIC with the same architecture as the DTA-2125. |

DTA-2125 Bird's Eye View