## DVB/ASI Input+Output Adapter for PCI Bus

- Input and Output at Full 214 Mbps

- 8-MB Input Buffer, 8-MB Output Buffer

- Time Stamping

## FEATURES

- High-speed input and output, compliant to DVB/ASI-C as defined in DVB document A010 rev 1 and EN50083

- Parallel operation of input and output at the full DVB/ASI bit-rate range from 0 to 214 Mbit/s

- Adaptive cable equalisation

- Optional time stamp per packet

- Synchronised and raw receive modes

- Automatic recognition and adjustment of inverted DVB/ASI input signals

- Counters for bit-rate measurement, 8B/10B code violations and synchronisation errors

- LED indicator shows lock and synchronisation status of input circuitry

- 8-Mbytes input buffer for large jitter tolerance; independent 8-Mbytes output buffer

- Double-buffering: DVB/ASI output available on two BNC connectors

- Inverted DVB/ASI for special tests

- Continuous mode or burst mode

- PCI rev 2.2, 32 bit, 66 MHz

#### **KEY ATTRIBUTES**

| Parameter                              | Value          |  |  |  |  |

|----------------------------------------|----------------|--|--|--|--|

| Physical Layer                         | DVB/ASI-C      |  |  |  |  |

| DVB/ASI Connector                      | 75 Ω BNC (3x*) |  |  |  |  |

| Transmit Bit Rate                      | 0214 Mbit/s    |  |  |  |  |

| Transmit Bit Rate Resolution           | <1 bit/s       |  |  |  |  |

| Transmit Bit Rate Stability            | ±10 ppm        |  |  |  |  |

| Maximum Transmit Jitter**              | 70 ns p-p      |  |  |  |  |

| Input Bit Rate                         | 0214 Mbit/s    |  |  |  |  |

| Input Return Loss                      | 17 dB          |  |  |  |  |

| Error Free Cable Length                | 300m max       |  |  |  |  |

| * 1. target Ou datible buffanad autout | ·              |  |  |  |  |

1x input, 2x doubly-buffered output

\*\* In continuous mode

- Comes with free:

- Windows-2000/XP device driver

- Linux Software Development Kit

- API for developing custom applications

- Example streamer and grabber code

- DtGrabber: Windows grabber program

## **APPLICATIONS**

- Universal DVB/ASI input/output adapter for PC-based applications that record, play and/or process MPEG-2 transport streams

- iTV server

- IP-to-DVB and DVB-to-IP gateway

#### **PCI-BUS CHARACTERISTICS**

| PCI rev 2.2, 32 bit, <b>66 MHz</b> , |  |

|--------------------------------------|--|

| Master/Target, Universal 3.3V/5V     |  |

#### **RELATED PRODUCTS**

| Туре    | Description                             |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|

| DTA-100 | DVB/ASI Output Adapter for PCI Bus      |  |  |  |  |

| DTA-120 | DVB/ASI Input Adapter for PCI Bus       |  |  |  |  |

| DTC-300 | Transport-Stream Player <b>Software</b> |  |  |  |  |

| DTC-320 | Real-Time Analyser <b>Software</b>      |  |  |  |  |

| DTC-7X3 | "Ray" Stream Station                    |  |  |  |  |

# DTA-140

## **Table of Contents**

| 1. | General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | 1.1. Typical Application       3         1.2. Free Software       3         1.3. Commercial Applications       3         1.4. Block Diagram       4         1.4.1. PCI-9056 Bus Interface       4         1.4.2. Master Control       4         1.4.3. Transmit FIFO       4         1.4.4. Clock Synthesizer       4         1.4.5. ASI Transmit Logic       4         1.4.6. Equaliser       5         1.4.7. ASI Receive Logic       5         1.4.8. Receive FIFO       5         1.5. References       5         1.6. Document Overview       5                  |   |

| 2. | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7 |

|    | 2.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| 3. | Transmitting Data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 |

|    | 3.1. Buffer Model       10         3.1.1. Single-Buffer Model       10         3.1.2. Double-Buffer Model       10         3.1.3. Multiple Buffers       11         3.1.4. Transmit FIFO       11         3.2. Synchronisation       11         3.2.1. DMA-Driven       11         3.2.2. Transmission-Driven       12         3.3.8 Uffer Management       12         3.3.1. Ping-Pong, DMA-Driven       12         3.3.2. DMA-Driven, Start Up       13         3.3.3. Ping-Pong, Transmission-Driven       13         3.3.4. Transmission-Driven Start Up       14 |   |

| 4. | Receiving Data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 |

|    | 4.1. Buffer Model       15         4.1.1. Single-Buffer Model       15         4.1.2. Double-Buffer Model       15         4.1.3. Multiple Buffers       16         4.2. Synchronisation       16         4.3. Ping-Pong Buffering       16         4.3.1. Start Up       17         4.4. Packet Alignment       17         4.4.1. Fixed Buffer Structure       17         4.4.2. Switching Receive Mode       17                                                                                                                                                     |   |

|                                                            | 18                                      |

|------------------------------------------------------------|-----------------------------------------|

| -                                                          |                                         |

| Configuration Space                                        | 19                                      |

| Target Address Space                                       |                                         |

| 6.1. General Registers                                     |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

| 6.2. Iransmit Registers                                    | 27                                      |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

| 6.2.5. Transmit FIFO Load (18h)                            | 33                                      |

| 6.2.6. Transmit Diagnostics (1Ch)                          | 33                                      |

|                                                            |                                         |

| 6.2.8. Transmit-FIFO Data (40h7Ch)                         | 34                                      |

| 6.3. Receive Registers                                     |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

| 6.3.4. Receive Diagnostics (TCh)                           | 39                                      |

| 6.3.5. Receive Loop-Back Data (20h)                        | 40                                      |

| 6.3.0. Receive Valid Count (30n)                           | 40<br>41                                |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

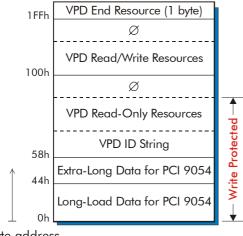

| 7.3. VPD Read-Only Resources                               | 42                                      |

|                                                            |                                         |

|                                                            |                                         |

| <b>v</b>                                                   |                                         |

| Hardware Details                                           | 46                                      |

| 8.1. Aspects of DMA                                        |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

|                                                            |                                         |

| 8.3.3. Scheduling Latency<br>8.3.4. Compensating Latencies | 50                                      |

|                                                            | <ul> <li>4.5.1. Block Diagram</li></ul> |

#### Copyright © 2002-2003 by DEKTEC Digital Video B.V.

DEKTEC Digital Video B.V. reserves the right to change products or specifications without notice. Information furnished in this document is believed to be accurate and reliable, but DEKTEC Digital Video assumes no responsibility for any errors that may appear in this material.

## **1. General Description**

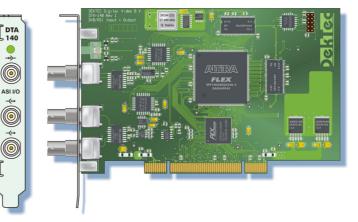

The DTA-140 is a PCI adapter that combines a doubly-buffered DVB/ASI output and a flexible DVB/ASI input into a single-slot unit.

The input and output channel run independently from each other, both support the full DVB/ASI range<sup>1</sup> from 0 to 214 Mbit/s.

## **1.1. Typical Application**

The DTA-140 is typically deployed as a DVB/ASI Input/Output unit in an industrial PC<sup>2</sup>. The low cost and high performance of the PC are leveraged to create cost-effective digital-video solutions.

Figure 1. The DTA-140 enables the receiving and transmitting of DVB/ASI signals from a single PCI slot in a PC.

The DTA-140 is well-suited for applications that record and play-out DVB/ASI streams, and for real-time processing of MPEG-2 Transport Streams.

Examples of digital-video applications with the DTA-140 include:

- iTV inserter;

- DVB/SI or PSIP inserter;

- Bit-rate transcoder;

- Logo inserter;

- Advertisement inserter.

## 1.2. Free Software

The DTA-140 comes with the following freely downloadable software:

- Windows-2000/XP WDM driver;

- Linux device driver;

- <sup>1</sup> The carrier frequency of a DVB/ASI signal is 270 MHz. is. The maximum effective bit rate is 214 Mbit/s.

- <sup>2</sup> The DTA-140 can also be used in desktop or mobile PC, or any other platform that supports the PCI bus.

- DTAPI library, available both for Windows and Linux.

## Note

- The Linux device driver and DTAPI are part of the open-source Linux SDK.

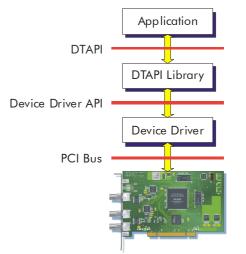

The device driver implements "low-level" operations that require direct access to the DTA-140 hardware, such as initiation and coordination of DMA transfers, handling interrupts and reading and writing of Vital Product Data (VPD, §7).

The DTAPI is a thin layer of user-mode software that packages the driver functions into an easy to use API.

Figure 2. Software stack for the DTA-140.

## **1.3. Commercial Applications**

DEKTEC offers a number of standard applications running on top of (amongst others) the DTA-140:

- DTC-300 streaming software;

- DTC-320 real-time analyser software.

Please refer to <u>www.dektec.com</u> for further details.

DEKTEC's commercial applications use a licensing system that ties the software to a specific DTA-140: the software will only run if an appropriate license code has been programmed into the on-board PROM.

Licenses can be purchased upfront, or the board can be upgraded in the field with the license code.

## 1.4. Block Diagram

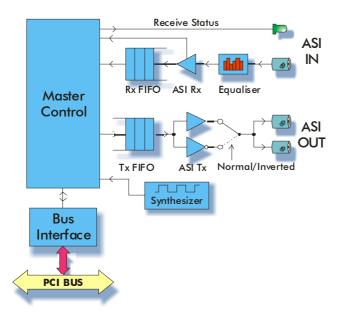

Figure 3 shows a conceptual block diagram of the DTA-140. Transport-stream data (and all other control data) enters the board via the *PCI-9056 Bus Interface*. The Master-Control block relays the packets to the *Transmit FIFO*. From there, an *ASI Adapter* translates the signals to the required DVB/ASI format.

Figure 3. Conceptual block diagram of the DTA-140.

The other functional blocks in the diagram support the various special functions offered by the DTA-140. The major functional units are discussed below in separate subsections.

## 1.4.1. PCI-9056 Bus Interface

The DTA-140 uses the PCI-9056 IC made by PLX for interfacing to the PCI Bus. The PCI-9056 also implements the DMA functions required for high-speed streaming of transport packets, with minimal host interaction.

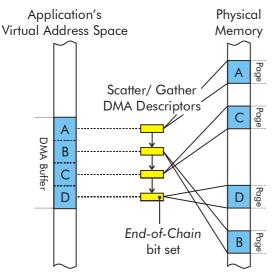

The PCI-9056 supports large host buffers with scatter/gather DMA mode. Such buffers may get fragmented through allocation / deallocation of memory by OS-components. A scatter/gather list glues the buffer together without requiring software intervention.

Whenever appropriate, this specification provides information on the way the PCI-9056's registers should be used on the DTA-140. To obtain more details on the operation of the PCI-9056, please refer to the PCI 9056 Data Book.

## 1.4.2. Master Control

Master Control is the block that supervises the DTA-140. It contains the control registers for configuring and operating the DTA-140. These registers are accessible from the PCI Bus. A description of the registers is given in §6.

## 1.4.3. Transmit FIFO

The Transmit FIFO is a large buffer (8-MBytes) for transport-stream data. The DTA-140 uses a standard SDRAM to implement this buffer economically.

The function of the Transmit FIFO is to enable the sustained generation of a low-jitter DVB/ASI stream. The Transmit FIFO compensates for latencies on the PCI Bus and for scheduling jitter of the software that generates the Transport Stream.

The DTA-140 supports a mode to automatically insert null packets when the Transmit FIFO underflows. In "raw" mode the DVB/ASI output signal is invalidated by stuffing with K28.5 characters.

## 1.4.4. Clock Synthesizer

The transport-stream clock for the DVB/ASI output channel is generated by a clock synthesizer. This circuit can be programmed to any bit rate between 0 and 214 Mbit/s, with a resolution of better then 1 bit/s.

## 1.4.5. ASI Transmit Logic

The DVB/ASI Transmit Logic converts the bytes coming from the Transmit FIFO into a DVBcompliant ASI signal which is buffered on two BNC connectors.

A special feature of the DTA-140 is a "Normal" / "Inverted" switch in the output circuitry. This enables the generation of a DVB/ASI signal with inverted polarity, for testing inputs for their ability to properly decode normal and inverted-polarity ASI signals.

## 1.4.6. Equaliser

The receive circuitry starts with a cable equaliser, which automatically adapts to equalise any cable length from zero to three hundred meters (Belden 8281 or equivalent).

## 1.4.7. ASI Receive Logic

The equalised signal is processed by a DVB/ASI receiver, which de-serialises the signal, synchronises to the MPEG-2 packet structure and writes the data into the Receive FIFO.

Special features of the ASI Receiver include:

- Time stamping: a sample of a reference clock is attached to each packet, so that the time of entrance of the packet can be derived.

- ASI polarity detection. Inverted DVB/ASI signals are automatically detected and corrected.

- Packet-size conversion, e.g. storage of 188byte packets, irrespective of the input packet size (188 or 204).

The status of the ASI Receiver is made visible to the outside world through the Receive Status LED.

## 1.4.8. Receive FIFO

The Receive FIFO is the counter part of the Transmit FIFO, but then for the receive channel. It has the same size (8-MBytes) uses standard SDRAM for its implementation.

The Receive FIFO provides a great deal of freedom for the receiving software. While the application processes data, new transportstream data is buffered in the Receive FIFO.

## 1.5. References

- Interfaces for CATV / SMATV Headends and Similar Professional Equipment, DVB DOCUMENT A010 rev.1, May 1997 – This is the original DVB document that specifies physical interfaces for the interconnection of signal processing devices for professional digital-television equipment. One of the interfaces described is DVB/ASI.

DVB document A010 document has also

been issued as CENELEC EN50083-9.

- ISO/IEC 13818-1, Information technology Generic coding of moving pictures and associated audio information: Systems, April 27<sup>th</sup>, 1995, also known as "MPEG-2 Systems" – Specification of the structure of a MPEG-2 Transport Stream.

- DTAPI: C++ API for DTA-series of Digital-Video PCI-Bus Cards, DEKTEC Digital Video B.V., 2001 – Specification of **DTAPI**: the C++ interface to access the DTA-140 functions at a higher level of abstraction than would be possible using direct devicedriver calls.

- PCI 9056 Data Book, PLX Technology, V0.91b, February 2002 – Specification of the PCI 9056, the chip used on the DTA-140 to interface with the PCI bus. Use this document if you need to program the PCI-9056 directly, e.g. when writing a custom device driver.

The latest version of this document is available on line at <u>http://www.plxtech.com</u>.

- PCI Local Bus Specification, Revision 2.2, December 18, 1998 – Formal specification of the protocol, electrical, and mechanical features of the PCI bus.

## 1.6. Document Overview

This specification describes the details relevant for operating the DTA-140. The information herein is primarily intended for device driver writers and for software developers that have to access the DTA-140 directly from a real-time operating system.

The WDM device driver and DTAPI library encapsulate many programming details of the DTA-140. Users of DTAPI may find this document useful for providing background information, but do not need to master each and every detail.

- Section 1 introduces the main features of the DTA-140.

- Section 2 describes the physical interfaces of the DTA-140. For the DVB/ASI output, this section explains the two DVB/ASI output modes: burst- and continuous- mode.

- Section 3 provides a detailed description of synchronisation and buffer-management issues to stream data with the DTA-140 in an efficient and reliable way.

- Section 4 does the same for synchronisation and buffer management in the Receive channel.

- Section 5 lists the PCI Configuration-Space registers supported by the DTA-140.

- Section 6 describes the operational registers on the DTA-140. These registers can be

used to control and monitor the streaming of digital-video data.

- Section 7 defines the structure of Vital Product Data (VPD) as supported by the DTA-140 and other DEKTEC PCI cards.

- Finally, Section 8 examines a number of hardware details that are irrelevant for most applications, yet important to applications that require the ultimate in performance

## 2. External Interfaces

## 2.1. Overview

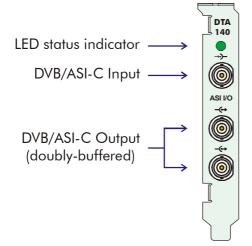

The lay-out of the DTA-140's PCI bracket is shown in Figure 4 below.

Figure 4. DTA-140 physical interfaces.

The LED indicator provides the status of the DVB/ASI input beneath it.

The DVB/ASI output is doubly buffered. The same signal is available on two BNC connectors.

## 2.2. DVB/ASI Input

The upper BNC connector on the DTA-140 bracket is the DVB/ASI input.

## 2.2.1. Applicable Standard

The DVB/ASI input is compliant to the Asynchronous Serial Interface on coaxial cable (ASI-C), as defined in DVB Document A010.

The input connector is  $75-\Omega$  BNC.

## 2.2.2. LED Status Indicator

The bi-colour (red/green) LED above the input connector displays the status of the DVB/ASI-C input signal.

The status is indicated using a combination of colour-encoding and a flashing pattern. Table 1 shows the various indications. The flash-pattern pictures show the colour of the LED over time. Grey represents "LED off".

| Table 1. LED Status Indications |                                                                             |  |  |

|---------------------------------|-----------------------------------------------------------------------------|--|--|

| LED Status                      | Meaning                                                                     |  |  |

| No                              | data                                                                        |  |  |

|                                 | No signal                                                                   |  |  |

|                                 | ASI carrier without TS,<br>or data rate too low<br>(less than about 1 kbps) |  |  |

| Error co                        | onditions                                                                   |  |  |

|                                 | No lock                                                                     |  |  |

|                                 | Code violation(s)                                                           |  |  |

|                                 | Receive-FIFO overflow                                                       |  |  |

| Valid data                      |                                                                             |  |  |

|                                 | Valid data but unknown<br>packet size                                       |  |  |

|                                 | Valid 188-byte packets                                                      |  |  |

|                                 | Valid 188-byte packets,<br>inverted ASI                                     |  |  |

|                                 | Valid 204-byte packets                                                      |  |  |

|                                 | Valid 204-byte packets,<br>inverted ASI                                     |  |  |

| Spe                             | ecial                                                                       |  |  |

|                                 | Receive-channel reset                                                       |  |  |

## Note

- The LED indication may also be overruled by software (refer to §6.1.1.7, §6.3.1.7).

The error conditions "No lock" and "Code violation" may be caused by a non-DVB/ASI signal (e.g. a SMPTE signal), a badly attached BNC connector, a coax cable of poor quality or a cable that's too long.

Connecting a cable to the DTA-140 almost certainly leads to a temporary "No lock" (red) indication.

The valid-data indications show packet size and inverted-ASI status. If the DVB/ASI input signal is recognised as inverted DVB/ASI, then a very short flash, only just noticeable, interrupts the normal packet-size indication.

## 2.2.3. LED Power-Up Sequence

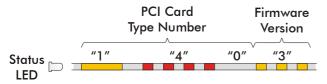

Just after power-up, the LED flashes a few times to indicate that the board is initialising. During this short period, the usual meaning of the LED indications does not apply. Instead, the LED pattern shows the board type and the firmware revision. An example start-up pattern is shown in Figure 5 below.

Figure 5. Power-up pattern for DTA-140 with (as example) firmware version 3.

## 2.3. DVB/ASI Output

The bottom two BNC connectors on the DTA-140 bracket is the DVB/ASI input.

#### 2.3.1. Applicable Standard

The DVB/ASI outputs are compliant to the Asynchronous Serial Interface on coaxial cable (ASI-C), as defined in DVB Document A010.

The output connectors is  $75-\Omega$  BNC.

#### 2.3.2. Transmission Jitter

DVB/ASI is characterised by a fixed symbol rate (27 MSymbol/s), but a variable transport rate. Special stuff characters (K28.5) are inserted to fill up the difference.

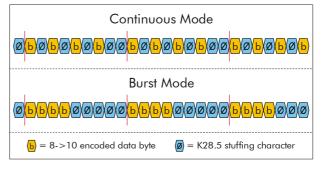

The 'real' data  $(8 \rightarrow 10 \text{ encoded bytes})$  and K28.5 stuff characters can be distributed over time in different ways. The DTA-140 supports two modes:

- Continuous Mode. MPEG-2 transport packets are spread evenly over time.

- Burst Mode. Packets are sent in bursts.

Figure 6 below illustrates these two modes. Short 4-byte packets are used in the figure to make the point. In reality, packet bursts consist of 188 or 204 consecutive bytes.

#### 2.3.2.1. Continuous Mode

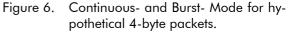

Continuous Mode is the recommended mode for normal operation. The DTA-140 limits the amount of transmission jitter to the theoretical minimum of  $\pm 35$  ns.

In DVB/ASI some jitter is necessarily introduced because:

- DVB/ASI characters align to a 27-MHz grid (transmission time is "quantised"), and

- The DVB/ASI specification requires that each MPEG-2 Sync character has to be preceded by at least two K28.5 stuffing characters.

- Figure 7. Jitter in the DVB/ASI output stream.  $\varnothing = K28.5$  stuffing character

- $\begin{array}{ll} T_{_{\alpha\nu}} & \mbox{Average time between two characters.} \\ T_{_{\alpha\nu}} \mbox{is the reciprocal of the transport rate:} \\ 8/R_{_{TS}} \mbox{ (factor 8 to get time between bytes).} \end{array}$

- $T_{i,pp}$  Peak-to-peak jitter interval = 70 ns

- t<sub>i</sub> Jitter of a single byte: time difference between average and actual position of an encoded DVB/ASI output byte.

The DTA-140 hardware ensures that the DVB/ASI characters are always output within the 70-ns time interval labelled  $T_{j,pp}$ , corresponding to a maximum jitter of ±35 ns.

#### 2.3.2.2. Burst Mode

The DTA-140 supports Burst Mode for special test applications, e.g. to check whether certain equipment with a DVB/ASI input accepts packets transmitted in bursts.

In Burst Mode, all 188 or 204 bytes in a packet are sent in one continuous data burst, without interspersed stuff bytes. The period between the end of a packet and the start of the next packet is stuffed with K28.5 characters.

#### Note

- In Burst Mode, the data bytes within a packet are sent in a burst, but the packets as a whole are distributed smoothly over time (no bursts of packets).

- If the transmission mode is **Raw**, the DTA-140 is ignorant of the packet size, and Burst Mode is not supported.

## 3. Transmitting Data

This section discusses *transmission* of MPEG-2 transport packets using the DTA-140, with the focus on *real-time* operation, this is the avoidance of "gaps" in the transmitted stream. Refer to Section 4 for a similar treatise on *reception* of MPEG-2 data.

## 3.1. Buffer Model

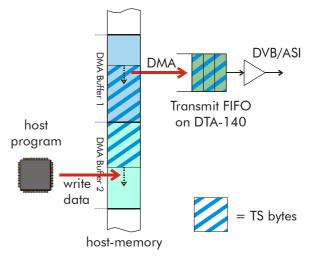

Transport-stream data to be transmitted by the DTA-140 is buffered in a cascade of two buffers:

- 1. The DMA Buffer, located in host memory. The host processor writes transport packets into this buffer.

- 2. The *Transmit FIFO*, which is an 8-Mbytes hardware buffer located on the DTA-140.

The DMA Controller on-board of the DTA-140 transfers the data from DMA Buffer to the Transmit FIFO. This data transfer incurs hardly any overhead for the host processor.

#### Notes

- Data can also be transferred from DMA Buffer to Transmit FIFO by direct PCI-read cycles, but this is far less efficient. Refer to §8.1.1 for a discussion.

- Details of the structure of DMA buffers (like scatter-gather), are described in §8.1.2.

From the viewpoint of the DMA Buffer, one process is writing in the buffer (host processor) and one process is reading from the buffer (DMA controller). Obviously, for correct data transfer, these processes must be synchronised to each other.

## 3.1.1. Single-Buffer Model

The first (and simplest) buffer model is to use a single DMA Buffer, and to alternate DMA- and host access to this buffer:

- While the host processor is writing data to the DMA Buffer, the DMA Controller remains idle.

- While the DMA Controller reads data from the DMA Buffer, the host processor remains idle.

This option is sub-optimal, but not as bad as it may seem. The DMA phase is relatively short, because DMA is very fast (>100 MByte/s).

## Example

- The output transport rate is 40 Mbit/s (5 MByte/s) and the data-transfer size is 1 MByte. Then the length of the DMA phase is 10 ms, while the length of the processing phase is as long as 190 ms. Just 5% of time is "lost" with transferring data.

The single-buffer model may break down in the following cases:

- At very high output rates, e.g. 200 Mbps.

- When the PCI Bus is heavily loaded, e.g. by data transfers for other DEKTEC cards. This may significantly increase the data-transfer time.

## 3.1.2. Double-Buffer Model

In the double-buffer model, the DMA Buffer is segmented into two sub-buffers: DMA Buffer 1 and DMA Buffer 2. The DMA Controller writes data to one sub-buffer, and in parallel the host processes packets from the other sub-buffer.

Figure 8. Tx double-buffer model. The DMA Controller reads data from DMA Buffer 1, while the host writes new data into DMA Buffer 2.

Figure 8 shows a snapshot of the double-buffer model in action. The buffer is split in DMA Buffer 1 and DMA Buffer 2, together forming one circular buffer. The blue-hatched area represents data that has been written to the buffer earlier.

Deklec

MPEG-2 data in DMA Buffer 1 is transferred to the Transmit FIFO by the DMA Controller on the DTA-140. At the same time, new packets are written in DMA Buffer 2 by the program running on the host.

If all of the data in DMA Buffer 1 has been read, <u>and</u> DMA Buffer 2 has been filled completely, the function of both DMA Buffers is swapped.

## 3.1.3. Multiple Buffers

The double-buffer model can be generalised to a scheme with N DMA buffers. Each process handles one DMA Buffer. When a process is done with one buffer it continues with the next buffer, unless the other process is still busy with that buffer.

This specification will not dig deeper into transmission schemes with more than two DMA Buffers.

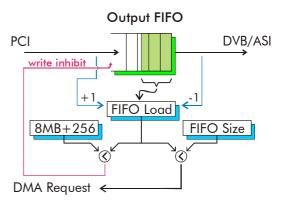

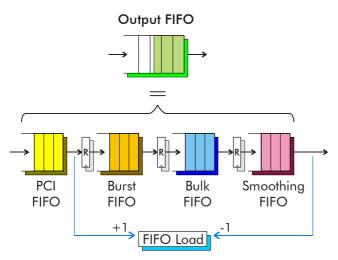

## 3.1.4. Transmit FIFO

The contents of the DMA Buffer are transferred to the *Transmit FIFO* on-board of the DTA-140. The Transmit FIFO converts the write bursts to a smooth output stream: The hardware reads bytes at the output side of the Transmit FIFO reads bytes at a constant rate – the transportstream rate – and converts the data bytes to DVB/ASI format.

For most applications, the Transmit FIFO can be considered a large conventional FIFO that can buffer 8-Mbytes of data. The maximum load of the Transmit FIFO can be reduced artificially through the Transmit-FIFO-Size register (§6.2.4).

#### Notes

The Transmit-FIFO-Size register does not determine the 'real' Transmit-FIFO size: The actual size of the Transmit FIFO is always 8 Mbytes (dependent on SDRAM size; §6.2.4). The Transmit-FIFO-Size register is the highwater mark that controls demand for DMA. Whenever the Transmit-FIFO load becomes greater or equal than the value in the Transmit-FIFO-Size register, the DTA-140 disables DMA until the Transmit-FIFO load drops below Transmit-FIFO Size again.

- It is hard to envisage an application that benefits from a reduced Transmit-FIFO Size. Therefore, most applications can simply program Transmit-FIFO Size to its maximum of 8 Mbytes.

- The hardware implementation of the Transmit FIFO is more complex than suggested by the model described above; Refer to §8.2 for particulars. The implementation details may be relevant for special applications, e.g. if one wants to achieve a low end-to-end delay at a low bit rate. Most regular applications need not bother about the finer points of the Transmit-FIFO implementation.

## 3.2. Synchronisation

The host processor generates transport packets into a DMA Buffer, while the DTA-140 reads the packets from the buffer and transmits them. Obviously, for a continuous Transport Stream, packet generation must be synchronised to packet transmission.

The DTA-140 transmission hardware supports two synchronisation methods:

- DMA-driven: §3.2.1;

- Transmission-driven: §3.2.2.

## 3.2.1. DMA-Driven

With DMA-Driven synchronisation, the host software locks generation of new packets to the completion of the last DMA transfer:

- 1. Host writes packets in DMA Buffer;

- 2. DMA Controller transfers data to DTA-140;

- 3. Host waits for DMA completion;

- 4. Go to Step 1.

When the host generates packets faster than the DTA-140 can transmit them, which must be the case for sustained operation without discontinuities, it seems that the Transmit FIFO on the DTA-140 would overflow.

However, DMA-driven synchronisation still works reliably because the DTA-140 hardware implements *demand-mode* DMA: DMA transfers are requested on the PCI Bus only as long as the DTA-140's Transmit FIFO has empty

buffer space left. When the FIFO becomes fully loaded<sup>3</sup>, the DMA process stalls. When FIFO space is available again, DMA resumes.

In other words: The Transmit FIFO <u>cannot</u> overflow in DMA-driven operation. The hand-shaking hardware prevents this from happening.

#### 3.2.2. Transmission-Driven

An alternative method of synchronisation is *Transmission Driven*: the generation of new packets is locked directly to the transmission of (previously-computed) packets.

- Initial load of packets (>x) is written to the Transmit FIFO;

- 2. Host starts transmission;

- 3. Host computes x new packets;

- 4. (In parallel to step 3) Host tracks number of transmitted packets and waits until *x* packets have been sent.

- 5. The x new packets are transferred to Transmit FIFO.

- 6. Go to Step 3.

The number of transmitted packets can be tracked using the so-called *Periodic Interrupt*, which is generated precisely every  $2^{21}$  cycles of the 27-MHz reference clock (this is: about once every 77.7 ms). The number of packets transmitted in this time interval is easily computed

by multiplying the packet rate by  $\frac{2^{21}}{27*10^6}$

#### Example

- Suppose 188-byte packets are transmitted at 40 Mbps, corresponding to a packet rate of 26596 transport packets per second. Multiplying by 77.7 ms yields the number of packets transmitted between two periodic interrupts: 2066.

So, after each periodic interrupt the program may write 2066 new packets to the DTA-140. The example above uses approximations. In practice, the synchronisation method will work correctly in the long run only if the *full fractional* part ("bits behind the comma") is taken into account. Otherwise, slight timing errors may accumulate and cause underflow or overflow in time.

Taking into account "all bits" involves using in the computations the full 32-bits value programmed in the Transmit-Clock (§6.2.3) register. As the periodic interrupt and the transmit clock are derived from the same master 27-MHz clock oscillator, the number of packets transmitted can be tracked exactly.

## 3.3. Buffer Management

This section discusses how to manage DMA Buffers such that synchronisation of packet generation by the host and packet transmission by the DTA-140 is achieved.

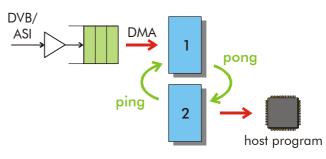

## 3.3.1. Ping-Pong, DMA-Driven

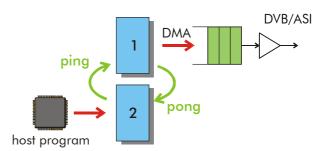

As explained in §3.1, efficient streaming of data to the DTA-140 requires at least two DMA Buffers. The host program computes new packets and writes them to one buffer. At the same time, the DMA Controller on the DTA-140 reads data from the other buffer. When <u>both</u> DMA is done <u>and</u> a new buffer with packet data has been filled, the DMA Buffers swap function. This process continues ad infinitum.

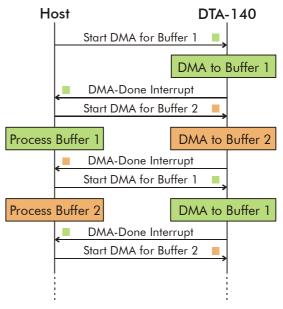

The use of two buffers that swap function after each cycle – also known as *Ping-Pong* buffering – is illustrated in Figure 9.

Figure 9. Ping-Pong buffering. The host writes packets in one buffer, while the DMA Controller reads packets from the other buffer. When both are finished, the "Ping-Pong" swap is executed.

<sup>&</sup>lt;sup>3</sup> "Fully loaded" in the sense that the load of the Transmit FIFO has become greater or equal than the value programmed in the FIFO-Size register.

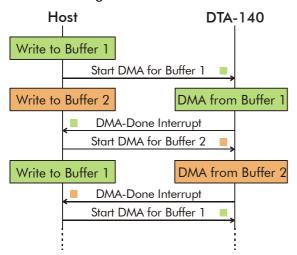

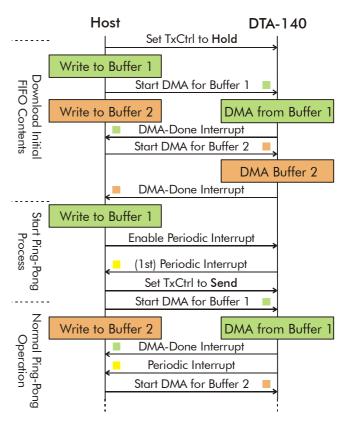

DMA-Driven flow control in a double-buffering scheme is illustrated in the message-sequence chart shown in Figure 10.

Figure 10. Ping-Pong buffer management using DMA-Driven flow control. After the host has filled a buffer and DMA on the other buffer is done, the buffers swap function.

The DMA-Done Interrupt is the handshake signal. It triggers the host to compute new packets and to initiate a new DMA transfer.

#### Note

- While waiting for the DMA-Done Interrupt, it is opportune for a device driver to sleep the process and give another process a chance to run.

It is instructive to ponder on the limiting factor in the Ping-Pong process: Host or DMA?

In the beginning, when the Transmit FIFO is not filled yet, the host will be the bottle neck. DMA transfers complete quickly, because DMA is only constrained by the PCI Bus.

After some time, when the Transmit FIFO is filled, DMA will become the limiting factor. The effective average rate of DMA will drop to the transmit rate, because of demand-mode DMA (Refer to §3.2.1). The host has to wait for the DMA-Done Interrupt before it can execute the next *Ping-Pong* swap.

## 3.3.2. DMA-Driven, Start Up

The robustness of the start-up phase of the Ping-Pong process can be improved by pre-

loading the Transmit FIFO with data before starting the Ping-Pong process.

This can be accomplished with the Transmit-Control field (§6.2.1.4) in the Transmit-Control register. Preloading is enabled by setting Transmit Control to **Hold** and issuing DMA transfers until the Transmit FIFO is (almost) filled. Then, Transmit Control is set to **Send**. The DTA-140 starts packet transmission and the Ping-Pong process may begin.

The controlled start-up method prevents potential underflow of the Transmit-FIFO in the startup phase<sup>4</sup>.

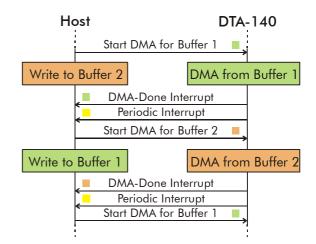

## 3.3.3. Ping-Pong, Transmission-Driven

The Ping-Pong buffering scheme can also be used in combination with Transmission-Driven flow control. Figure 11 shows two Ping-Pong cycles using Transmission-Driven synchronisation, assuming that the process has already stabilised.

Figure 11. Ping-Pong buffer management using Transmission-Driven flow control. The buffers swap function when both the DMA-Done Interrupt and the Periodic Interrupt have occurred.

The most obvious difference with DMA-Driven flow control is that the host software now has to wait for <u>both</u> DMA done <u>and</u> the periodic

<sup>&</sup>lt;sup>4</sup> If the process is started with Transmit Control set to Send, the Transmit FIFO may underflow early in the process (e.g. due to PCI-Bus latency), because no buffer load has been accumulated yet for compensation.

interrupt before proceeding with the next Ping-Pong cycle<sup>5</sup>.

A minor complication specific to Transmission-Driven flow control is that, in general, the number of packets transmitted between two Periodic Interrupts is not integer. The number of packets computed in cycle N must be rounded to the nearest integer. The length of the DMA transfer in cycle N+1 must be adapted to this size.

#### Note

- In Transmission-Driven flow control it makes no sense to artificially reduce the FIFO size. The FIFO-Size register should be programmed to its maximum value.

## 3.3.4. Transmission-Driven Start Up

The start-up procedure for Transmission-Driven flow control is somewhat more complicated then the procedure for DMA-Driven flow control.

In the start-up phase, the Transmit FIFO has to get an initial load. Figure 11 shows an example start-up procedure in which two DMA-Buffer loads are transferred to the Transmit FIFO.

#### Note

- This example uses initial loading in the "Ping-Pong way". A method with a single buffer could have been used too.

The start-up scenario proceeds through the following steps, assuming that the board and DMA Buffers have been properly initialised.

- Host sets TxCtrl to Hold. This enables DMA, but no packets will be transmitted yet.

- 2. Host fills DMA Buffer 1 with packets, and starts DMA.

- 3. Host fills DMA Buffer 2, while the DTA-140 reads DMA Buffer 1 in parallel.

4. Host waits for DMA-Done interrupt for DMA Buffer 1, then starts DMA for DMA Buffer 2.

Figure 12. Start-up phase of Ping-Pong buffer management with Transmission-Driven flow control. In this scenario, the initial load of the Transmit FIFO is set to 2 times the size of the DMA Buffer.

Host waits for DMA-Done interrupt for DMA Buffer 2. The Transmit FIFO now has an initial load.

6. Host fills DMA Buffer 1 with packet data. This will be the first buffer that is transferred in "Normal Ping-Pong Operation".

- 7. Host enables Periodic Interrupts and waits for the occurrence of the first Periodic Interrupt.

- 8. Host sets TxCtrl to Send.

- 9. Normal Ping-Pong Operation is entered.

<sup>&</sup>lt;sup>5</sup> Under normal circumstances, DMA is much faster than packet transmission. This means that the DMA interrupt will almost always occur long before the periodic interrupt arises. However, for robustness the software should also wait for the DMA interrupt.

## 4. Receiving Data

This section describes several aspects of *receiving* MPEG-2 transport packets with the DTA-140.

The discussion will be quite similar to Section 3's treatise on transmission, only with the processes working in the opposite direction.

## 4.1. Buffer Model

When receiving an MPEG-2 Transport-Stream with the DTA-140, the incoming data is buffered in a cascade of two buffers:

- 1. The Receive FIFO, which is an 8-Mbytes hardware buffer located on the DTA-140.

- 2. The DMA Buffer, which is a "software" buffer located in host memory. Data in the DMA Buffer is available for further processing by the host processor.

Just like data transfers for transmission, the DMA Controller on the DTA-140 also transferred data from Receive FIFO to DMA Buffer, without much overhead for the host processor.

#### Notes

- Data can also be transferred from Receive FIFO to DMA Buffer by direct PCI-read cycles, but this is far less efficient. Refer to §8.1.1 for a discussion.

- Details of the structure of DMA buffers (like scatter-gather), are described in §8.1.2.

From the viewpoint of the DMA Buffer, one process is writing in the buffer (DMA controller) and one process is reading from the buffer (host processor). These processes must be synchronised to each other, otherwise DMA may overwrite data that is just being processed.

## 4.1.1. Single-Buffer Model

As with transmission, the simplest buffer model is to use a single DMA Buffer, and to alternate DMA- and host access to this buffer:

- While the DMA Controller is writing data to the DMA Buffer, the host application remains idle.

- While the host processes the data from the DMA Buffer, the DMA controller remains idle.

The single-buffer model is sub-optimal, but not as bad as it may seem. The DMA phase is relatively short, because DMA is very fast (>100 MByte/s). In the "processing phase", new incoming data can be easily accommodated in the Receive FIFO.

## Example

- Data is entering the system at 40 Mbit/s (5 MByte/s) and the data-transfer size is 1 MByte. Then the length of the DMA phase is 10 ms, but the length of the processing phase is as long as 190 ms. Just 5% of time is "lost" with transferring data.

The single-buffer model may break down in the following cases:

- At very high input rates, e.g. 200 Mbps.

- When the PCI Bus is heavily loaded.

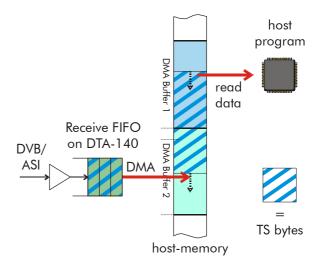

## 4.1.2. Double-Buffer Model

In the double-buffer model, the DMA Buffer is segmented into two sub-buffers: DMA Buffer 1 and DMA Buffer 2. The DMA Controller writes data to one sub-buffer, and in parallel the host processes packets from the other sub-buffer.

Figure 13 shows a snapshot of the doublebuffer model in action. DMA Buffer 1 and DMA Buffer 2 together form one circular buffer. The blue-hatched area represents Transport-Stream data that still has to be processed by the host program. MPEG-2 data in DMA Buffer 1 is processed by the program running on the host. At the same time, the DMA Controller transfers new packets from the Receive FIFO on the DTA-140 to DMA Buffer 2.

If all of the data in DMA Buffer 1 has been read, <u>and</u> DMA Buffer 2 has been filled completely, the function of the DMA Buffers is swapped.

## 4.1.3. Multiple Buffers

The double-buffer model can be generalised to a scheme with N DMA buffers. Each process handles one DMA Buffer. When a process is done with one buffer it continues with the next buffer, unless the other process is still busy with that buffer.

This specification will not dig deeper into reception methods that use more than two DMA Buffers.

## 4.2. Synchronisation

The DTA-140 reads transport packets, and the host processor processes these packets. Obviously, packet reception must be synchronised to packet processing.

The DTA-140 reception hardware is tailored for *DMA-Driven* synchronisation: The host software locks packet processing to the completion of DMA transfers.

DMA transfers from Receive FIFO to DMA buffer can be initiated <u>before</u> the Receive FIFO contains sufficient data to complete the DMA transfer. The DMA-done interrupt signals to the host software that another buffer load is available for processing by the application.

DMA-driven synchronisation works reliably because the DTA-140 hardware implements demand-mode DMA: DMA transfers are requested on the PCI Bus only as long as the DTA-140's Receive FIFO has data available. When the FIFO becomes empty, the DMA process stalls. When new data enters the Receive FIFO again, DMA process restarts.

In other words: The Receive FIFO <u>cannot</u> underflow in DMA-driven operation. The handshaking hardware prevents this from happening.

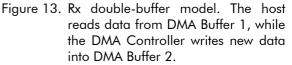

## 4.3. Ping-Pong Buffering

This section discusses the combination of double buffering and DMA-driven synchronisation.

The use of two buffers that swap function after each cycle – also known as *Ping-Pong* buffering – is illustrated in Figure 14.

Figure 14. Ping-Pong buffering. The DMA Controller writes packets from the Receive FIFO into one buffer, while the host reads packets from the other buffer. When both are finished, the "Ping-Pong" swap is executed.

DMA-Driven flow control in a double-buffering scheme is illustrated in the message-sequence chart shown in Figure 15.

Figure 15. Ping-Pong buffer management using DMA-Driven flow control. After the host has read a buffer and the DMA write to the other buffer is done, the buffers swap function.

The DMA-Done Interrupt acts as handshake signal. It triggers the host to read and process new packets, and to initiate a new DMA transfer.

#### Note

- While waiting for the DMA-Done Interrupt, the device driver should sleep the process and give another process a chance to run.

## 4.3.1. Start Up

The following procedure is recommended to start the Ping-Pong process:

- 1. Allocate DMA Buffers and associated scatter/gather DMA descriptors.

- 2. Clear the Receive FIFO on the DTA-140 by setting RxClfFifo in the Receive-Control register (§6.3.1.10). This will also reset the Receive Control (§6.3.1.3) to **Idle**.

- Initiate the first DMA transfer from Receive FIFO to DMA Buffer. As the Receive FIFO is still in idle mode, no data will be transferred yet.

- 4. Set Receive-Control to Rcv.

At this time, transport packets are allowed to enter the Receive FIFO. Shortly thereafter, the first data will be transferred to the DMA Buffer.

5. Normal Ping-Pong Operation has started!

## 4.4. Packet Alignment

The DTA-140 supports alignment of transport packets in the DMA buffer:

- MPEG-2 sync bytes (0x47) are stored at 32bit aligned byte positions;

- After setting Receive-Control to **Rcv**, the first data transferred to the DMA Buffer will start at a packet boundary.

Packet alignment is provided for in Receive Modes **St188**, **St204** and **StMp2**, but not in **StRaw**. In raw mode, the DTA-140 does not take the packet structure into account, and sync bytes may appear at any relative address.

## 4.4.1. Fixed Buffer Structure

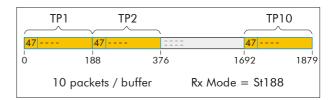

Packet alignment opens up the possibility of a fixed packet lay-out in the DMA Buffer(s).

Hereto, the Receive Mode must be set to **St188** or **St204**, and the buffer size must be chosen a multiple of the packet size.

Figure 16 shows an example of packet alignment in an 1880-byte DMA-Buffer (10 packets), with Receive Mode set to **St188**.

Figure 16. Transport packets stored at fixed locations. The buffer size must be a multiple of the packet size.

#### Notes

- Receive Mode StMp2 cannot be used reliably for packet alignment in a DMA Buffer: When the size of the incoming transport packets changes dynamically, alignment will likely break.

- It is good software-engineering practice to test for packet alignment, even if packets "should always be aligned". If the test would fail, the input channel should be reset and input processing restarted.

## 4.4.2. Switching Receive Mode

The DTA-140 supports *dynamic* switching of Receive Mode, this is going from one mode to another while, at the same time, data is being stored in the Receive FIFO. However, such dynamic switching may <u>break</u> packet alignment.

## Note

- Dynamic switching may even break 32-bit alignment of MPEG-2 sync bytes.

If you want to switch Receive Mode, while reliably maintaining packet alignment (and 32bit alignent), a channel reset is required:

- 1. Set Receive Control to Idle;

- 2. Reset receive channel;

- 2. Set Receive Mode to the desired value;

- 3. Set Receive Control to Rcv.

An inevitable side effect of the use of a channel reset is the "loss" of a number of incoming packets.

## 4.5. Time Stamping

This section discusses the use of time stamping, as a method to measure the time of entrance of incoming transport packets. The measurement is made available to the application in the form of *time stamps*, attached to the packets.

Applications of time-stamping include:

- Real-time processing of transport streams, e.g. for PCR correction.

- Synchronisation of multiple incoming transport streams in (re-)multiplexers.

- Measurement of real-time packet-delivery jitter.

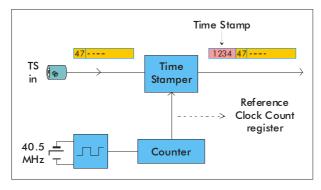

## 4.5.1. Block Diagram

Time stamps are derived from a reference clock counter, running at 40.5 Mhz. Every time a packet enters the DTA-140, a sample of the counter is taken and the value is prepended to the packet.

Figure 17. Schematic block diagram of the time-stamping hardware.

The value of the reference-clock counter can also be observed from the PCI bus, by reading the Reference-Clock-Count register (§6.1.4).

## 4.5.2. Time-Stamp Format

Time stamping can be enabled by setting the RxTimeStamp the (§6.3.1.4) in the Receive-Control register. Receive Mode must be one of **St188**, **St204** or **StMp2**.

#### Note

- Time stamping is not supported in raw mode (**StRaw**).

Time stamps are stored in Little-Endian format into the 4 bytes that are placed before the packet, as shown in Table 2.

| Table 2. Time Stamps – Packet Format |          |                                        |  |  |  |

|--------------------------------------|----------|----------------------------------------|--|--|--|

| Addr⁵                                | Value    | Description                            |  |  |  |

| 00h                                  | bit 70   |                                        |  |  |  |

| 01h                                  | bit 158  | Time stamp in 4 bytes                  |  |  |  |

| 02h                                  | bit 2316 | nine sidinp in 4 byles                 |  |  |  |

| 03h                                  | bit 3124 |                                        |  |  |  |

| 04h                                  | 47h      | MPEG-2 Sync                            |  |  |  |

| :                                    | :        | Transport-packet header<br>and payload |  |  |  |

| BFh                                  | XX       | Last byte of packet                    |  |  |  |

The application program can find the location of the time stamps by synchronising to the MPEG-2 Sync bytes.

Another option is to choose a buffer size that is a multiple of the packet + time-stamp size (e.g. a multiple of 192 for **St188**). The first four bytes of the buffer will then always contain a time stamp. See also  $\S4.4.1$ .

<sup>6</sup> Relative address in packet.

## 5. Configuration Space

The DTA-140 acts as a single logical PCI Bus device. It implements the configuration registers required for identifying the device, control PCI Bus functions, and provide PCI Bus status.

Table 3 displays the address map of registers defined in configuration space:

- Black fields indicate configuration registers

supported by the DTA-140.

- Red-text cells represent registers supported by the PCI bridge chip, but not used for operating the DTA-140.

- Grey-text cells represent registers defined in the PCI Local Bus Revision 2.2 specification, but not supported on the DTA-140.

| Table 3. Configuration Space – Address Map |                                                                          |                              |                          |                            |  |  |

|--------------------------------------------|--------------------------------------------------------------------------|------------------------------|--------------------------|----------------------------|--|--|

| Address Offset                             | Byte                                                                     |                              |                          |                            |  |  |

| Address Offser                             | 3                                                                        | 2                            | 1                        | 0                          |  |  |

| 00h                                        | Devie                                                                    | ce ID                        | Venc                     | lor ID                     |  |  |

| 04h                                        | Status F                                                                 | Register                     | Comman                   | d Register                 |  |  |

| 08h                                        |                                                                          | Class Code                   |                          | Revision ID                |  |  |

| 0Ch                                        | BIST                                                                     | Header Type                  | Latency Timer            | Cache Line Size            |  |  |

| 10h                                        | PCI Base Address                                                         | 0; used for memory-m         | apped configuration re   | egisters (PCI 9056)        |  |  |

| 14h                                        |                                                                          | PCI Base Addre               | ess 1; not used          |                            |  |  |

| 18h                                        | PCI Base Ac                                                              | ldress 2; used for mem       | ory-mapped operatior     | nal registers <sup>7</sup> |  |  |

| 1Ch                                        |                                                                          | PCI Base Address 3; not used |                          |                            |  |  |

| 20h                                        |                                                                          | PCI Base Address 4; not used |                          |                            |  |  |

| 24h                                        |                                                                          | PCI Base Address 5; not used |                          |                            |  |  |

| 28h                                        |                                                                          | Cardbus CIS Point            | ter; not supported       |                            |  |  |

| 2Ch                                        | Subsys                                                                   | tem ID                       | Subsystem                | Vendor ID                  |  |  |

| 30h                                        | E                                                                        | xpansion ROM Base Ac         | ldress Register; not use | ed                         |  |  |

| 34h                                        |                                                                          | Reserved                     |                          | Next_Cap = 40h             |  |  |

| 38h                                        |                                                                          | Rese                         | rved                     |                            |  |  |

| 3Ch                                        | Maximum Latency                                                          | Interrupt Line               |                          |                            |  |  |

| 40h                                        | Power Management Capabilities; not used Next_Cap = 48h Capability IE     |                              |                          |                            |  |  |

| 44h                                        | Power Management Register; not used                                      |                              |                          |                            |  |  |

| 48h                                        | Hot Swap; not used Next_Cap = 4Ch Capability ID = 06h                    |                              |                          |                            |  |  |

| 4Ch                                        | VPD; used for manufacturing / service Next_Cap = 00h Capability ID = 03h |                              |                          |                            |  |  |

| 50h                                        | VPD; used for manufacturing / service                                    |                              |                          |                            |  |  |

Table 4 shows a short description of the registers in configuration space.

$<sup>^7\,</sup>$  Operational registers are mapped in "Local Address Space 0" of the PCI 9056.

| Table 4. Configuration Space – Register Overview |      |     |         |                                                                                                                                                                                 |  |

|--------------------------------------------------|------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Register                                         | Bits | RW* | Value   | Short Description                                                                                                                                                               |  |

| Vendor ID                                        | 16   | R   | 10B5h   | Identifies PLX as manufacturer of the PCI interface chip.                                                                                                                       |  |

| Device ID                                        | 16   | R   | 9056h   | Identifies the PCI interface chip (PCI 9056).                                                                                                                                   |  |

| Command Register                                 | 16   | RW  | -       | Provides coarse control on the ability to generate and respond to PCI cycles.                                                                                                   |  |

| Status Register                                  | 16   | RWC | -       | Status of PCI-Bus relevant events.                                                                                                                                              |  |

| Revision ID                                      | 8    | R   | 0       | Revision number of your DTA-140.                                                                                                                                                |  |

| Class Code                                       | 24   | R   | FF0000h | Generic function of the DTA-140.                                                                                                                                                |  |

| Cache Line Size                                  | 8    | R   | 16      | System cache line size in units of 32-bit words.                                                                                                                                |  |

| Latency Timer                                    | 8    | RW  | -       | Amount of time in PCI-Bus-clock units that the DTA-140 may retain ownership of the PCI Bus.                                                                                     |  |

| Header Type                                      | 8    | R   | 0       | Specifies layout of configuration addresses 10h through 3Fh and single / multiple functions.                                                                                    |  |

| BIST                                             | 8    | R   | 0       | PCI Built-In Self Test (BIST).                                                                                                                                                  |  |

| PCI Base Address 0                               | 32   | RW  | -       | Memory attributes and base memory address for memory ac-<br>cesses to PCI-9056 registers                                                                                        |  |

| PCI Base Address 2                               | 32   | RW  | -       | Memory attributes and base memory address for memory ac-<br>cesses to Local Address Space 0, which is used to access the<br>DTA-140's operational registers (Refer to Table 5). |  |

| Subsystem Vendor ID                              | 16   | R   | 14B4h   | Identifies the manufacturer of the DTA-140.<br>Subsystem Vendor ID and Subsystem Device ID are leased from<br>Philips BE.                                                       |  |

| Subsystem Device ID                              | 16   | R   | D140h   | Identifies the PCI card as a DTA-140.                                                                                                                                           |  |

| Interrupt Line                                   | 8    | RW  | -       | Interrupt line routing information.                                                                                                                                             |  |

| Interrupt Pin                                    | 8    | R   | 01h     | Interrupt pin used by the DTA-140.                                                                                                                                              |  |

| Minimum Grant                                    | 8    | R   | 10h     | Length of time (in 250-ns units) DTA-140 would like to retain master ship of the PCI Bus.                                                                                       |  |

| Maximum Latency                                  | 8    | R   | 1Ah     | Frequency in which the DTA-140 would like to gain access to the PCI Bus.                                                                                                        |  |

## 6. Target Address Space

The DTA-140's operational registers are mapped in Local-Address Space 0 of the PCI 9056. The PCI Base address of these registers is specified in BAR2. All accesses to the operational registers shall be 32-bit transfers.

|                | Table 5. Operational Registers – Memory Map |               |                    |                   |  |  |  |

|----------------|---------------------------------------------|---------------|--------------------|-------------------|--|--|--|

|                | Byte                                        |               |                    |                   |  |  |  |

| Address Offset | 3 2 1 0                                     |               |                    |                   |  |  |  |

|                |                                             | General       |                    |                   |  |  |  |

| 00h            |                                             | Genero        | ıl Control         |                   |  |  |  |

| 04h            | 0000 0000                                   | 0000 0000     | 0000 0000          | General Status    |  |  |  |

| 08h            | 0000 0000                                   | 0000 0000     | 0000 0000          | 0 0 Programming   |  |  |  |

| 0Ch            |                                             | Reference-    | Clock Count        |                   |  |  |  |

| 10h 7Ch        | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

|                |                                             | Transmit (Tx) |                    |                   |  |  |  |

| 80h            | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| 84h            | 0000 0000                                   | 0000 0000     | 00000              | Transmit Control  |  |  |  |

| 88h            | 0000 0000                                   | 0000 0000     | 00000              | Transmit Status   |  |  |  |

| 8Ch            |                                             | Transn        | nit Clock          |                   |  |  |  |

| 90h            | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| 94h            | 0000 0000                                   |               | Transmit FIFO Size |                   |  |  |  |

| 98h            | 0000 0000                                   |               | Transmit FIFO Load |                   |  |  |  |

| 9Ch            |                                             | Transmit      | Diagnostics        |                   |  |  |  |

| A0h            | 0000 0000                                   | 0000 0000     | 0000 0000          | Tx Loop-Back Data |  |  |  |

| A4h BCh        | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| C0h FCh        |                                             | Transmit      | FIFO Data          |                   |  |  |  |

|                |                                             | Receive (Rx)  |                    |                   |  |  |  |

| 100h           | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| 104h           | 0000 0000                                   | 0 0           | Receive Contro     | l                 |  |  |  |

| 108h           | 0000 0000                                   | 000000        | Receive            | Status            |  |  |  |

| 10Ch 114h      | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| 118h           | 0000 0000                                   |               | Receive FIFO Load  |                   |  |  |  |

| 11Ch           | Receive Diagnostics                         |               |                    |                   |  |  |  |

| 120h           | 0000 0000                                   | 0000 0000     | 0000 0000          | Rx Loop-Back Data |  |  |  |

| 124h 12Ch      | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| 130h           |                                             | Receive V     | alid Count         |                   |  |  |  |

| 134h           |                                             | Receive Vic   | lation Count       |                   |  |  |  |

| 138h 13Ch      | 0000 0000                                   | 0000 0000     | 0000 0000          | 0000 0000         |  |  |  |

| 140h 17Ch      |                                             | Receive       | FIFO Data          |                   |  |  |  |

| Table 6. Operational Registers – General Registers |                                                                 |      |    |    |                                       |  |

|----------------------------------------------------|-----------------------------------------------------------------|------|----|----|---------------------------------------|--|

| Register                                           | Field         Bit Pos         #         RWC*         Short Desc |      |    |    | Short Description                     |  |

| General Control                                    | PE                                                              | 0    | 1  | RW | Serial EEPROM Program Enable          |  |

|                                                    | PRE                                                             | 1    | 1  | RW | Serial EEPROM Protect Register Enable |  |

|                                                    | Reset                                                           | 2    | 1  | W  | Reset DTA-140 circuitry               |  |

|                                                    | reserved                                                        | 3    | 1  | R  | Not used                              |  |

|                                                    | PerIntEn                                                        | 4    | 1  | RW | Periodic-Interrupt Enable             |  |

|                                                    | reserved                                                        | 75   | 3  | R  | Not used                              |  |

|                                                    | FirmwRev                                                        | 158  | 8  | R  | Firmware Revision                     |  |

|                                                    | TypeNum                                                         | 2316 | 8  | R  | Type Number: 140 for DTA-140          |  |

|                                                    | LedControl                                                      | 24   | 1  | RW | Take over LED Control                 |  |

|                                                    | LedGreen                                                        | 25   | 1  | RW | State of Green LED                    |  |

|                                                    | LedRed                                                          | 26   | 1  | RW | State of Red LED                      |  |

| General Status                                     | reserved                                                        | 30   | 4  | R  | Not used                              |  |

|                                                    | PerInt                                                          | 4    | 1  | RC | Periodic Interrupt                    |  |

| Programming                                        | TRST                                                            | 0    | 1  | RW | Control of TRST# pin                  |  |

|                                                    | TDO                                                             | 1    | 1  | R  | Status of EPC2 TDO pin                |  |

|                                                    | TMS                                                             | 2    | 1  | W  | Control of EPC2 TMS pin               |  |

|                                                    | TCK                                                             | 3    | 1  | RW | Control of EPC2 TCK pin               |  |

|                                                    | TDI                                                             | 4    | 1  | RW | Control of EPC2 TDI pin               |  |

|                                                    | ProgramEpc                                                      | 5    | 1  | RW | Program EPC2                          |  |

| Reference Clock                                    | RefClkCnt                                                       | 310  | 32 | R  | Reference-Clock Count                 |  |

| Table 7. Operational Registers – Transmit Registers |             |         |    |      |                                               |  |  |

|-----------------------------------------------------|-------------|---------|----|------|-----------------------------------------------|--|--|

| Register                                            | Field       | Bit Pos | #  | RWC* | Short Description                             |  |  |